environment 2 Back End Ecole de microélectronique 2017 IN2P3 gregorybertoloneiphccnrsfr Introduction 2 Motivations Give a start up methodology for digital back end flow for Implementation of digital blocks for small ID: 935870

Download Presentation The PPT/PDF document "Introduction to the digital flow in mixe..." is the property of its rightful owner. Permission is granted to download and print the materials on this web site for personal, non-commercial use only, and to display it on your personal computer provided you do not modify the materials and that you retain all copyright notices contained in the materials. By downloading content from our website, you accept the terms of this agreement.

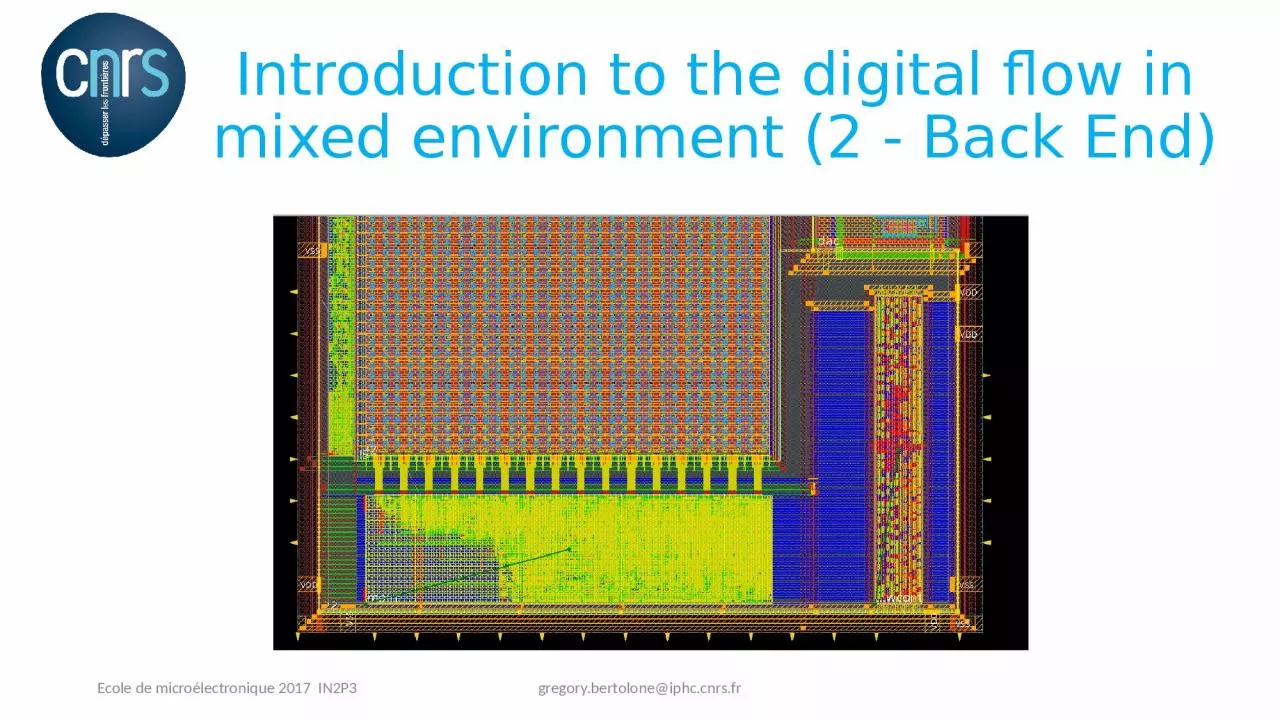

Slide1

Introduction to the digital flow in mixed

environment (2 - Back End)

Ecole de microélectronique 2017 IN2P3

gregory.bertolone@iphc.cnrs.fr

Slide2Introduction

2

Slide3Motivations

Give a start up methodology for digital back end flow for Implementation of digital blocks for small logic core (~ 50 k instances) Mixed S

ignal ASICs with a Digital on Top (DoT) / Mixed Signal (MS) flow context

Open Access (OA) based designTiming Constraint design

3

Slide4Back End Digital Flow

4

netlist (.v) map on

std

cells and IP

Synthesis (Genus)

Functional netlist

(.v, .

vhd

, .

sv

)

Place and Route

(

Innovus

)

Technology Files

(liberty,

qrc

techfile

, abstract, ...)

Timing Constraints (

sdc

)

Layout in OA /

gds

Netlist in Verilog

Sdf

file for post extraction simulations

Signoff VerificationDRC and LVS checking(PVS)STA (Timing Check) with Tempus

Formal Verification

(LEC)

Timing

not met

Slide5Prerequisites for Back End Digital Flow

Interoperable PDKFunctional netlist

Abstract ViewLiberty filesTiming Constraint

MMMC view

5

Slide61.Interoperable PDK

The Design Kit could be used in the Virtuoso flow or in the Digital flow Common OA techfile

Common qrc techfile for the extraction

=> a common cds.lib for digital tools

and

analog

tools

6

Slide72.Synthesizable functional netlist

For the same register, use only rising edge OR falling edge, not bothTest Bench coding style is forbiddenNo reference for reading or writing in a text file No display message

Assertion, probing or specific tools simulator commands (nc_mirror, …) are bannedYou can not delay a signal from xxx ns; only clock cycle could be use to synchronize your signals in your design.

i_ck80 <= NOT i_ck80 AFTER 6.25 ns

7

Slide83. Abstract view in OA format for Std

Cells / IPThese abstracts could be : provided by the foundry or the IP providergenerated by the user with the virtuoso abstract generator

generated from the lef files provided by the foundryo

a2lef –lef

my_IP.lef

–lib

my_IP_OA_library

8

Slide94. Liberty Files

Foreach cell of a library, these files describe: The ports (input and output, power)The type of cells : buffer, inverter, and gate, io

pads , …The operating conditionThe power consumption (optional)The timing modelling

These Liberty files are given by the foundry or could be generated for custom IP with LIBERATE tool (see Xavier Liopart

talk in 2015)

9

Slide105. Timing constraints (Sdc

files )The sdc files (Synopsis Design Constraints) describe all the timing information between your design and the outside: what are the clocks signals? What are the relation between clocks ?

what is the delay between the signals and the clock? What is the input or output capacitance load ?What are the timing exceptions ?…..

By default, the time unit is the ns

10

Slide116. M

ulti-Mode Multi-Corner view

Multi M

ode : The chip have different functional modes (different clock speed, enable bit configuration, …)

=> One or more constraint modes associated with

sdc

files for each mode

M

ulti

C

orner

There is different library set (process corner typical

, slow, fast,

…) and RC corners for timing analysis (propagation delay, SI analysis)

=> Each delay corners combine liberty (.lib) for the

std

cells and QRC

techfiles

for the nets

=> MMMC view file combines constraint modes and delay corners to define different scenarios (“Analysis View”)

These analysis views are used for setup analysis and the hold during STA11

Slide12MMMC view: example

create_library_set -name

tlf_typical -timing liberty/tsl18fs120_tt_1p8v_25c.lib -

si Celtic/cells_tt_1p8v_25c.cdB

create_library_set

-

name

tlf_max

-timing

liberty/tsl18fs120_ss_1p62v_125c.lib

-

si

Celtic/cells_ss_1p62v_125c.cdB

create_library_set

-name

tlf_min -timing liberty/tsl18fs120_ff_1p98v_m40c.lib -si

Celtic/cells_ff_1p98v_m40c.cdBcreate_rc_corner -name Corner_RC_QRC -T 25

-qx_tech_file RCE_TS18SL_QRC_6M1L/qrcTechFile

create_delay_corner -name corner_ocv -rc_corner Corner_RC_QRC

-early_library_set tlf_min -

late_library_set tlf_max \-early_opcond_library

tsl18fs120_ff_1p98v_m40c -late_opcond_library tsl18fs120_ss_1p62v_125c \

-early_opcond ff_1p98v_m40c -

late_opcond ss_1p62v_125ccreate_constraint_mode -name

mode_no_latch -sdc_files sdc/constraint_no_latch.sdc create_constraint_mode -name mode_with_latch -sdc_files

sdc/constraint_with_latch.sdc create_analysis_view -name ocv_no_latch -

constraint_mode mode_no_latch -delay_corner

corner_ocvcreate_analysis_view -name ocv_with_latch -

constraint_mode mode_with_latch -delay_corner

corner_ocvset_analysis_view -setup

[list

ocv_no_latch

ocv_with_latch

]

-hold

[list

ocv_no_latch

ocv_with_latch

]

12

Slide13SDC files

Setup / HoldClock Inputs

OutputsTiming exceptions

13

Slide141. Setup and Hold checks (1/2)

The setup and hold timing checks are needed for proper propagation of data through the sequential cells. These checks verify that the data input is stable at the active clock edge.

Setup time = minimum time with data stable

before clock edgeHold time = minimum time with data stable

after

clock edge

14

Slide15Setup and Hold checks (2/2)

15

Slide16Warnings !

The sdc files guide the digital tools during synthesis, placement and routing to avoid setup or hold failure.So be careful when you write them !

All path should be constrained to enable their analysis.=> Unconstrained path can lead to “hidden” timing violations or “over design”

16

Slide172. Clock: declaration

Creating a clockcreate_clock command defines an ideal clock signal and specifies the ports or pin that are connected to the clock.Example : definition of a clock :

on port CLK with a 25ns period rising edge at 5 ns and falling edge at 12create_clock

[get_port CLK] -name

m_clk

-period

25 -

waveform

{5 12}

17

Slide18Clock: transition

Clock Transition (slew)

set_clock_transition 0.38 –rise clock_name

set_clock_transition

0.38

–fall

clock_name

18

Slide19Clock: uncertainty (skew)

Use the clock uncertainty to add margin for setup/hold check or take in account clock jitter and clock tree skew

set_clock_uncertainty

–setup 0.65 [get_clocks

m_clk

]

set_clock_uncertainty

–hold

0.65 [

get_clocks

m_clk

]

19

Slide203. Input: declaration

Input delayThe input delay describes the arrival time on a port relative to the clock. It could be for example the time needed for the data to go through combinational logic before the moduleUse the –max argument for setup and

–min for holdcreate_clock -period 15 -waveform {5 12} [

get_ports CLKP]set_input_delay -clock CLKP -max 6.7 [get_ports

INPA]

set_input_delay

-clock CLKP -min 3.0 [

get_ports

INPA]

20

Slide21Input: constraint

21

Max and min delays on input port.

Slide224. Output: declaration

Output delay :Use the set_output_delay command to set the output path delay value for the design

create_clock -period 20 -waveform {0 15} [get_ports CLKQ]set_output_delay -clock CLKQ -min -0.2 [

get_ports OUTC]set_output_delay -clock CLKQ -max 7.4 [

get_ports

OUTC]

22

Slide23Output : constraint

23

Max and min delays on

output port.

Slide24Output: load

Use the set_load command to define the output load (in pF)

set_load -max 0.500 [all_outputs]

set_load -min

0.250 [

all_outputs

]

Tips:

To select all

the inputs

all_inputs

To select all

outputs

all_outputs

24

Slide255. Timing exception

False path: When the designer wants to exclude a path (like reset) from the timing analysisset_false_path

-from [get_ports rstb]

Case analysisWhen a signal is fixed to a logic value (configuration register, enable for scan chain, …)

set_case_analysis

0

enable_latch

25

Slide26Synthesis(Genus)

Library SetupLoad Design / Elaborate

Constraints setupsyn_gen

syn_map and syn_opt

Write outputs

26

Slide27Synthesis flow (Genus)

Functional netlists (.v, .

vhd, .sv)

Technology Files

(liberty,

qrc

techfile

)

Timing Constraints (

sdc

)

Verilog netlist mapped on

std

cells and IP

LEC scripts for Formal verification

INNOVUS

GENUS

1.Library

Setup

2.Load

Design /

Elaborate

3.Constraint Setup

5.Synthesizing to gates

and optimize the netlist

6

.Write Outputs

4.Synthesizing to generic

27

Slide28Genus

To launch genus :linux:/> genus

-legacy_uiGenus could be launched in batch mode with a .tcl

scriptgenus

–

legacy_ui

–files

my_script.tcl

By default, the GUI is not visible

legacy_genus

:/>

gui_show

legacy_genus

:/>

gui_hide

To generate a template for synthesis flow

legacy_genus

:/>

write_template

-outfile my_tempate.tcl

28

Slide291. Synthesis: Library Setup

## setup the lib fileset_attribute

init_lib_search_path { my_PDK_path/Std_cells/liberty

} set_attribute

library

{tsl18fs120_tt_1p8v_25c.lib}

##

Provide

the

qrc_tech_file

set_attribute

qrc_tech_file

{

my_PDK_path

/QRC/

qrcTechFile} 29

Slide302. Synthesis : Load Design / Elaborate

# Load the design (Verilog, system Verilog or Vhdl files)

read_hdl –sv

PE_valid_region.sv read_hdl

–

vhd

reg_cmd.vhd

read_hdl

main.v

## elaborate

:

Create a unique Verilog

netlist for the design

e

laborate

main

## Verify undefined or black box module

check_design -unresolved

Respect a bottom up hierarchy when reading the design!

30

Slide313. Synthesis: Constraint Setup

legacy_genus:/> read_sdc top_cell.sdc

Must have no errors

31

Slide324. Synthesis : syn_generic

## Synthesizing to generic syn_generic

Design is map on custom genus cells

32

Slide33Synthesis : check sdc constraints

## check if all the ports are constraintsreport

timing -lint

Every warning have to be check

33

Slide345. Synthesis: syn_map and

syn_opt### map generic netlist to cell from the librarysyn_map

### optimize the netlist ( timing, power and area )syn_opt

34

Slide35Synthesis: Timing report

After each step (

syn_generic, syn_map,

syn_opt), do a timing reportreport

timing

35

Slack = timing margin

If slack <0 ?

Redo an optimization

Review your

sdc

file

Review your functional netlist

Slide36Synthesis: QOR

Before saving your design, do a qor(Quality Of Result) report : Gives information about timing, area, instances used, …

report

qor > my_qor.txt

36

legacy_genus

:/> report

qor

===========================================

Generated by: Genus(TM) Synthesis Solution 16.13-s036_1

Generated on: Apr 12 2017 05:47:02 pm

Module: main

Technology libraries: tsl18fs120_tt_1p8v_25c 1

physical_cells

Operating conditions: _nominal_

Interconnect mode: global

Area mode: physical library

============================================================Timing--------

Cost Critical Violating Mode Group Path Slack TNS Paths -------------------------------------------------main_clk 1072.6 0.0-------------------------------------------------Total 0.0 0

Instance Count--------------Leaf Instance Count 3148 Sequential Instance Count 1068 Combinational Instance Count 2080

Hierarchical Instance Count 18 Area----Cell Area 124386.304Physical Cell Area 0.000Total Cell Area (Cell+Physical) 124386.304Net Area 44730.429Total Area (Cell+Physical+Net) 169116.733

Slide376. Synthesis: Write Outputs

## write final netlist write_hdl

> main_m.v### write final sdc

write_sdc

>

main_m.sdc

### write

lec

files

write_do_lec

-

revised_design

main_m.v

>

rtl2final.lec.do

37

Slide38Synthesis: Summary

38

Slide39Place and Route (P&R)(

Innovus)Design Import

PreCTSCTSNanoRoute

and PostRouteCheck Timing

Save Design

39

Slide40Signoff Verification

P&R Flow

Gate level

netlist in verilog

Technology Files

( QRC

techfile

)

MMMC View Definition File

STA (Tempus)

OA libs

defined by a cds.lib

Synthesis

Layout (OA or

gds

)

+ netlist in

verilog

DRC/LVS (PVS)

Power Analysis (

Voltus

)

Innovus

1.Design Import

2.PreCTS Flow

3.CTS Flow

4.PostCTS Flow

5.Timing Checks

40

6

.Design Export

Slide41Innovus: start

vdi licence optionSame tools, but :

limited to 50k Instances.MMMC not available with this license use Tempus license to run MMMC

more licenses available at IN2P3.linux

:/>

innovus

-

lic_startup

vdi

To start full version

linux

:/>

innovus

linux

:/>

innovus

–log my_log -overwrite41

Slide42Innovus: GUI

Menus

Design Views :

FloorPlan

AMOEBA

Physical

Layer control Bar

Cursor Coordinates

Design Status

Tools

Name of the selected object

42

Slide43Innovus: Scripting vs GUI

GUI : easy way to discover the commands and the tool

more interactivity with the tools some commands are not accessible with the GUIScripting (.

tcl) not so easy to start writing a

tcl

script at the beginning

script could be executed in background

full option commands

script could be easily reused

Tips : Every

cmd

(Graphical and

scripted)

are automatically

transcripted

in the

innovus

.

cmd

file43

Slide441. Design Import

GUI Menus: File /Import Design

MMMC View

Power/Ground nets

OA reference libs:

Techfile

first, then others library

Synthesize netlist

Top cell name

To save/load your configuration in a .

globals

To import your design with

tcl

commands :

source

XXX.globals

init_design

44

Slide45MMMC: Browser

45

Slide46P&R: Some tools setup before PreCTS

Specify the process node (180 nm, 90n, …) to tune your parasitic extractionsetDesignMode

-process 180Specify the number of processor to usesetMultiCpuUsage

-localCpu

8

Check for

missing or inconsistent library and design

datacheck

checkDesign

–all

46

Slide472. PreCTS:

floorplaningGUI Menus: Floorplan /Specify Floorplan

47

Slide48PreCTS: Pins

placementGUI Menus: Edit / Pin Editor

Warnings ! Put your pins on the routing gridAvoid putting pin too close from stripes

Respect metal layer directionEven layer are verticalOdd layer are horizontal

48

Slide49PreCTS: IP/Block placement

Tcl command to place Macro Block and IPplaceInstance

<instance_name> <location> <orientation>Example

:

placeInstance

reg_row

50 12

R270

With the GUI, select your instance and move it with your mouse.

49

Slide50PreCTS: Power planning

Defines your stripes/rings

GUI Menus: Power / Power PlanningYou

can add Stripes (Horizontal or Vertical power lines)Rings (around core or Blocks)

2. When

your power planning is finished, route your powers nets with

sroute

command

.

50

Slide51PreCTS: layout before cells placement

pins

51

Stripes

rows

Slide52PreCTS:

std cells placementNew placer (GigaPlace) with

InnovusGigaPlace place your std cells and do a first routing before the Clock Tree Synthesis (CTS).

The router (trialRoute) is not DRC signOff, but it

is quick and give you a good idea of the feasibility of your design (timing + congestion)

52

Slide53PreCTS: Placement and optimization

Specify the top and bottom layer used for routingsetRouteMode

-earlyGlobalMaxRouteLayer 4

setRouteMode -earlyGlobalMinRouteLayer

1

Place your

std

cells

place_opt_design

Optimize your design if necessary

optDesign

-

preCTS

53

Slide54place_opt_design vs placeDesign

54

Slide55Layout after placement

55

Slide563. CTS Flow

Clock Trees are mandatory for synchronous design: one buffer can not drive every flip flopthe clock should arrived almost at the same time at each flip flop => minimize the Clock skew

Clock Tree Synthesis step (CTS) is done with CCOPT tool inside

innovus

ccopt_design

(-

cts

)

56

Slide57ccopt_design or

ccopt_design -cts ?

ccopt_design - ctswith vdi

licenceneed and optimization afterccopt_design

with full

innovus

license

57

Slide58CTS flow

Create a clock tree specification according to your sdc

create_ccopt_clock_tree_spec –filename

ccopt.specsource

ccopt.spec

Run

CCOpt

or

CCOpt

-CTS

ccopt_design

Report timing and optimize if necessary (slack <0)

timeDesign

–

postCTS

optDesign

-

postCTS

timeDesign – postCTS –hold

optDesign –postCTS -hold

58

Slide59CTS flow

Report on clock trees.

report_ccopt_clock_trees –filename

clock_trees.rpt

report_ccopt_skew_groups

–

filename

skew_groups.rpt

Open

the

CCOpt

Clock

Tree

Debugger (CTD)

Window

. ctd_win

Alternatively, use the “CCOpt Clock Tree Debugger” entry in the main GUI menu (

Clock menu)

59

Slide60CTD window

clock trees

clock skew

60

Slide61Post CTS layout

61

Remarks : the routing is done with

trialRoute = > some drc errors are possible after routing

Slide624. PostCTS flow:

NanoRoute NanoRoute is a timing driven router. It’s also take in account :

Crosstalk and Signal IntegrityDRC / LVS issueprocess antenna violationnets and via optimization (add multi cut for example)

62

Slide63Setting for NanoRoute

Specify your Top and Bottom

layer for routingsetNanoRouteMode -

routeTopRoutingLayer 4setNanoRouteMode

-

routeBottomRoutingLayer

1

Turn on

SI-driven routing

setsignoffOptMode

-

fixGlitch

true

|

false

setNanoRouteMode

-

routeWithSiDriven

true63

Slide64Setting for NanoRoute

Specify antenna fixing optionsetNanoRouteMode -

drouteFixAntenna truesetNanoRouteMode -routeAntennaCellName

« my_diode » setNanoRouteMode

-

routeInsertAntennaDiode

true

When you have setup

NanoRoute

, route your design

Tcl

command

:

routeDesign

64

Slide65NanoRoute GUI

Diode Cell name

Min and max Routing layer

Routing options

65

Slide66PostRoute: Verify the routing

after each routing, check :the connectivity (open, short)verifyConnectivity

DRC rules (metal spacing, cells overlap, …)verifyGeometryprocess antenna

verifyProcessAntenna You can see the result of your checks :

in the Violation Browser

in your console

o

n your layout (errors are marked with white cross)

Does not replace DRC and LVS !!!

66

Slide67PostRoute: Violation browser

67

Slide68PostRoute: Fixing routing errors

Most of the time, redoing a routeDesign is enoughIf some errors remains, try to :Add or increase the strength of the cells

Add diodes Delete path or nets with errors and re-routes themMove your std cells to avoid DRC errors spacing

Tips : use “editDelete

–net

” to remove a routed net

editDelete

-net

PE_region

/

Imux_region

/FE_RN_6_0

routeDesign

68

Slide69PostRoute: Optimization

Post Route optimization flow : setExtractRCMode

-engine postRoute

setExtractRCMode -effortLevel signoff

timeDesign

-

postRoute

optDesign

-

postRoute

-setup

timeDesign

-

hold

-

postRoute

optDesign

-postRoute -hold

Tools setup

Timing analyzing and optimization

69

Slide70PostRoute: Add Filler cells

addFiller

-cell

feedth

feedth3 feedth9

-prefix

FILLER

# do an eco route to fix DRC issue after Filler insertion

ecoRoute

-

fix_drc

When your design has no violation, add filler cells

70

Slide715. Signoff Timing check with Innovus

Tcl commands :timeDesign

–signofftimeDesign –

signoff -hold

GUI menu :

Timing/Report Timing

71

Slide72Timing Debugging

GUI menu :

Timing/Debug Timing

TCL Script:

report_timing

-

machine_readable

>

top.mtarpt

load_timing_debug_report

top.mtarpt

72

Slide736. Save Design (1/2)

When timing checks (+ DRC, connectivity, …) are fine, Save the design in OA viewsaveDesign -cellview

{libname cellname viewname

} Export the final netlist

saveNetlist

main_EDI.v

Your design is mapped on abstract view ! Remaster abstract views to layout view if needed in virtuoso

73

Slide74Save Design (2/2)

Create an abstract of your block (in case of Digital On Top flow)save_abstract -

lib lib_name -view

abstractExport sdf for simulation

write_sdf

-

view

<analysis view name>

my_sdf_file.sdf

74

Slide75Summary of

Innovus flow

75

Slide76Digital On Top (DoT) flow

AoT vs DoTDoT Flow

Slide771. Analog On Top vs Digital On Top

Analog On Top (AOT)Top level of the design is

described with schematicTiming

between analog and digital block is

not

critical

=> The design

is

assembled

with

virtuoso

(

layout

XL flow)

Digital On Top (DOT)

Top

level of the design is

described with a netlist (in verilog if possible)Timing between blocks is critical

Mixed Signal blocks are placed as black boxes=> The design is assembled with Innovus

77

Slide782. DOT flow

Digital routed and analog blocks are taken as abstractAnalog Block must be Layout XL compliant, have a Boundary and if possible an abstractTo evaluate correctly the P-Cells, set this variable in your

linux shell : > setenv CDS_ENABLE_EXP_PCELL

TRUE

You need an

sdc

file for the top module (and each submodule)

You have to provide the OA library (and if possible the .lib) of your macro block

78

Slide79DoT: Bottom up vs Top Down

Bottom Up flow :You already have abstracts for your submodule and they are routed independently from the top

Top Down flowYou have to define your partition (submodules) and the timing budget assign to each partition. Innovus

creates library for each components. You route them later

79

Slide80Place and route flow for Dot

Same classical flow as a standard block for placement and routing of the top. Just consider macro block as “super std cells” Import design

Place your macro bloc (IP or other submodules)Route your powers and place your pins

Place std cells (if needed)

CTS (if needed)

NanoRoute

Save your design

exit

80

Slide81DoT: Example of rooted top module design

81

Abstract for submodules

Routed nets

Slide82DoT: Design Assembling for STA

Assembling your design allows innovus to “flatten” the abstracts of submodule into smaller and smaller basic bricks (like std cells or IP)

Restart innovusBefore loading your design, make every block unique

> set init_design_uniquify

1

Restore your Design

>

restoreDesign

-

cellview

{

lib_name

cell_name

view_name

}

82

Slide83DoT: Design

Assembling for STA

Assemble each module you want to flattenassembleDesign -

block {my_OA_lib my_celll

my_view

}

Respect a top down hierarchy for the assembling

This

view is only for timing analysis. Do not use it later for routing!

83

Slide84DoT: Example of a partially assembled design

84

“Assembled” module

Abstract for unassembled modules

Abstract for unassembled modules

Slide85DoT: Design Assembling for STA

Save your designsaveDesign

-cellview {lib_name cell_name

view_name}

This view is only for STA ! Do not use it for LVS !

Perform STA with

Innovus

or Tempus on the whole chip

timeDesign

or

report_timing

commands

85

Slide86Conclusion

86

Slide87Synthesis and P&R Flow

87

GENUS

1.Library

Setup

2.Load

Design /

Elaborate

3.Constraint Setup

5.Synthesizing to gates

and optimize the netlist

6

.Write Outputs

4.Synthesizing to generic

Innovus

1.Design Import

2.PreCTS Flow

3.CTS Flow

4.PostCTS Flow

5.Timing Checks

6

.Save Design

Technology Files

(liberty,

qrc

techfile

, abstract)

Functional netlist

(.v, .

vhd

, .

sv

)

Timing Constraints (

sdc

)

Layout in OA /

gds

Netlist in Verilog

Sdf

file for post extraction

simulations

Slide88DoT flow

AoT vs DoT :AoT based on a schematic Virtuoso flow

DoT based on a netlist Innovus flow

DoT and Mixed Signal P&R:

Same flow as a full Digital flow; just considers blocks as “special

std

cells” or IP

Do

assembleDesign

for STA checking

For analog block, need a timing modeling (.lib) if the block interact with pure digital modules

88

Slide89For further informations on Digital Flow:

About sdc : “Static Timing Analysis

for Nanometer Designs : a Practical Approach” from

J . Bhasker and Rakesh Chadha About Genus and

Innovus

tools

Cadence Support website

Cadence Rapid Adoption Kit (RAK)

Cadence Training

Genus,

Innovus

User Guide

89