PPT-CEDA Chapter

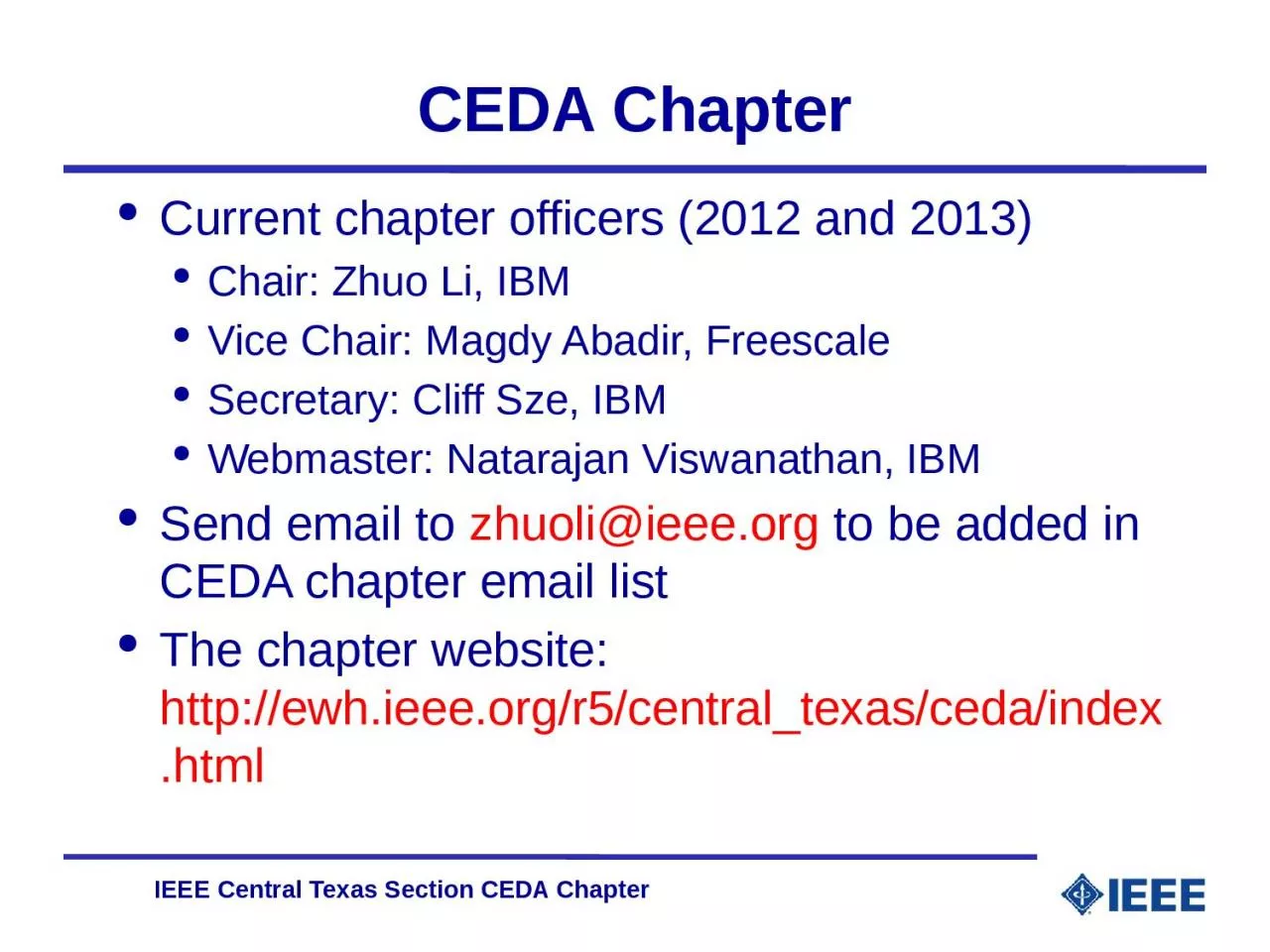

officers 2012 and 2013 Chair Zhuo Li IBM Vice Chair Magdy Abadir Freescale Secretary Cliff Sze IBM Webmaster Natarajan Viswanathan IBM Send email to zhuoliieeeorg

Download Presentation

"CEDA Chapter" is the property of its rightful owner. Permission is granted to download and print materials on this website for personal, non-commercial use only, provided you retain all copyright notices. By downloading content from our website, you accept the terms of this agreement.

Presentation Transcript

Transcript not available.