PDF-http://www.eecs.berkeley.edu/~kubitron/cs252

cs252S09 Lecture 92

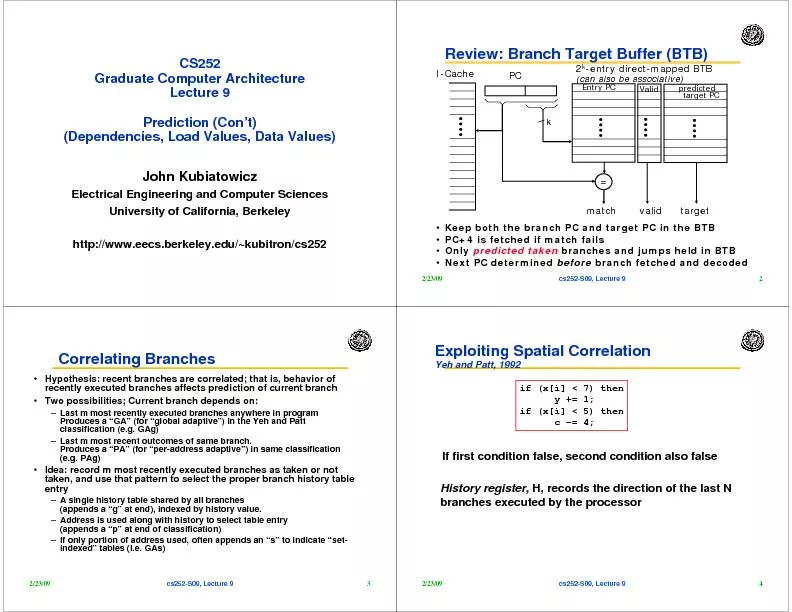

Keep both the branch PC and target PC in the BTB Entry PC target PC

22309

Two possibilities Current branch depends onProduces a

Download Presentation

"http://www.eecs.berkeley.edu/~kubitron/cs252" is the property of its rightful owner. Permission is granted to download and print materials on this website for personal, non-commercial use only, provided you retain all copyright notices. By downloading content from our website, you accept the terms of this agreement.

Presentation Transcript

Transcript not available.