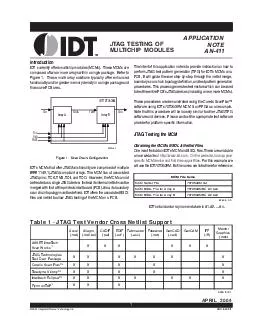

PDF-Application Note AN JTAG Testing of IDTs Multichip Modules Introduction IDT currently offers multichip modules MCMs

SO

lindy-dunigan

Published 2014-12-24 | 6754 Views

These MCMs are composed of two or more arrays within a single package Refer to Figure 1 These multiarray solutions typically offer enhanced functionality andor greater

Download Presentation

Download Presentation The PPT/PDF document "Application Note AN JTAG Testing of IDTs..." is the property of its rightful owner. Permission is granted to download and print the materials on this website for personal, non-commercial use only, and to display it on your personal computer provided you do not modify the materials and that you retain all copyright notices contained in the materials. By downloading content from our website, you accept the terms of this agreement.