PDF-Time ns clk previous stage master la

Author : briana-ranney | Published Date : 2015-05-16

brPage 1br brPage 2br brPage 3br brPage 4br Time ns clk 00 00 11 previous stage master latch slave latch brPage 5br

Presentation Embed Code

Download Presentation

Download Presentation The PPT/PDF document "Time ns clk previous stage master la" is the property of its rightful owner. Permission is granted to download and print the materials on this website for personal, non-commercial use only, and to display it on your personal computer provided you do not modify the materials and that you retain all copyright notices contained in the materials. By downloading content from our website, you accept the terms of this agreement.

Time ns clk previous stage master la: Transcript

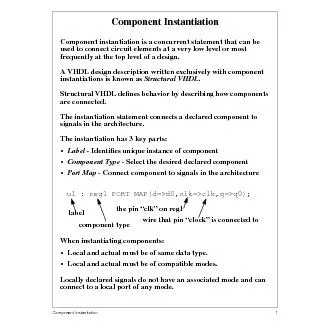

brPage 1br brPage 2br brPage 3br brPage 4br Time ns clk 00 00 11 previous stage master latch slave latch brPage 5br. Winifreds Virginia Stamford Hill Walter Reid Stanmore Warner Beach Stonebridge Washington Heights Stonebrigde Waterfall Stonehill Waterloo Sunford Watsonia S1 S1R1 never 11 R1 brPage 9br S1 Levelsensitive SR latch S1 Clk R1 brPage 10br 100 GHz 001 ns Period Freq 10 GHz 1 GHz 100 MH 01 ns 1 ns 10 ns 100 MH 10 MHz 10 ns 100 ns brPage 11br S1 Levelsensitive SR latch Clk R1 brPage 12br D latch DQ D latch 3 GN PW IN SC SD GN AGN MIC2 MIC1 SPK1 RXD SPK1 LOU DSP K LOUDSPK PWRKE EM O TX RTS DC SI SIMIO SI MV IMCLK SIM GN QUECTEL M95 SIM GN E6 10u SIM GN C2 33p C9 33p R12 1K Q4 C84 R14 100 PWRKE PW KE PWRKE PW KE R10 2K DDE XT C1 33p C1 33p C1 33p C1 10p ���u1 : reg1 PORT MAP(d=d0,clk=clk,q=q0);label component type wire that pin Sequential Circuits. Montek Singh. Sep 21, 2015. 2. Topics. Sequential Circuits. Latches. Flip Flops. Verilog . for sequential design. Example: A . simple counter. 3. Sequential Circuits. State. of system is . Last Lecture. module ex2(input . logic . a, b, c,. . output . logic . f);. logic . t; . // internal signal. always_comb. begin. . t = a & b;. . f = t | c;. end. endmodule. ISAs. . and MIPS. Steve Ko. Computer Sciences and Engineering. University at Buffalo. 2. Last . Time…. Computer . Architecture >> . ISAs. and RTL. Comp. . Arch. shaped by technology and . applications. Montek Singh. Sep 26, 2016. 2. Topics. Sequential Circuits. Latches. Flip Flops. Verilog design patterns for . sequential design. Examples. 3. Sequential Circuits. State. of system is . information stored/memorized. Register is built with gates, but has memory.. The only type of flip-flop required in this class – the D flip-flop . Has at least two inputs (both 1-bit): D and . clk. Has at least one output (1-bit): Q. Design. The Test Bench Concept. Project simulations. Behavioral/RTL – verify functionality. Model in VHDL/. Verilog. Drive with “force file” or . testbench. Post-Synthesis. Synthesized gate-level VHDL/. Digital Electronics. Flip-Flops & Latches. 2. This presentation will. Review sequential logic and the flip-flop.. Introduce the D flip-flop and provide an excitation table and a sample timing analysis.. TI BIOS CLK-PRD Multi-Threaded Systems 15 February 2018 Dr. Veton Këpuska 1 Why DSP/BIOS For most system developers today, more time is spent on software design than on hardware design . This is mainly due to the fact that most of the complex CIRCUIT CELLAR® er, I’ve noticed that many electricalthem quite complex, but they haven’t waveforms indicate the uncertainty ofuncertainty, because the uncertainty2. Note that the waveform Download PDF The Erectile Master™ eBook by Christian Goodman - A Digital Program For Men Designed to Overcome Erectile Dysfunction By Following Simple, Easy Exercises.

Download Document

Here is the link to download the presentation.

"Time ns clk previous stage master la"The content belongs to its owner. You may download and print it for personal use, without modification, and keep all copyright notices. By downloading, you agree to these terms.

Related Documents