PPT-Computer Organization and Design

Author : cheryl-pisano | Published Date : 2018-03-18

Transistors and all that a brief overview Montek Singh Oct 25 2017 Lecture 9 1 Todays Topics Where are we in this course Todays topics Why go digital E ncoding

Presentation Embed Code

Download Presentation

Download Presentation The PPT/PDF document "Computer Organization and Design" is the property of its rightful owner. Permission is granted to download and print the materials on this website for personal, non-commercial use only, and to display it on your personal computer provided you do not modify the materials and that you retain all copyright notices contained in the materials. By downloading content from our website, you accept the terms of this agreement.

Computer Organization and Design: Transcript

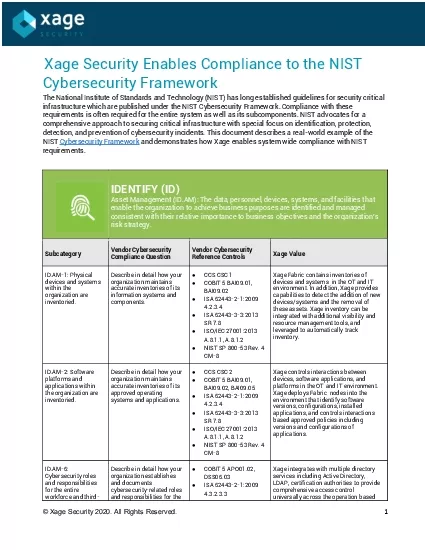

Transistors and all that a brief overview Montek Singh Oct 25 2017 Lecture 9 1 Todays Topics Where are we in this course Todays topics Why go digital E ncoding bits using voltages. Lampson Computer Science Laboratory Xerox Palo Alto Research Center Palo Alto CA 94304 Abstract Studying the design and implementation of a number of computer has led to some general hints for system design They are described here and illustrated by Slide . 1. Part V. Memory System Design. Feb. 2011. Computer Architecture, Memory System Design. Slide . 2. About This Presentation. This presentation is intended to support the use of the textbook . Facts. Charter Organization owns the unit . It also owns all the resources to include any trailers, troop camping gear, and treasury!. If a Troop leaves a Chartered Organization for another, the resources must be left behind pending any negotiated transfer agreements.. Power Tools for Nonprofits Conference . - November . 2018. Introductions. PAULA DESCANT MOORE. Deloitte Consulting. Agenda. SESSION. INTRODUCTION. 5 . minutes. PERSONA/. EXPERIENCE MAP. 30 . minutes. Learning Objectives. Defining . CyberSecurity. Why Should You Care?. Who Are Hackers (Yesterday vs. Today)?. Understanding Typical Hacking Exploits. CyberSecurity. Strategies: Protecting Your Organization. Introduction. Khaled N. Khasawneh, PhD Student. Department of Computer Science and Engineering. kkhas001@ucr.edu. Welcome!. 2. About me. Born and raised in . Jordan. Jordan University of Science & Technology, Jordan. access management with Single Sign-on SSO and Multi-Factor Authentication MFA universally across the operation with full visibility for auditability With Xage organizations can unify identity and acce S201David GoldschmidtEmail goldschmidtgmailcomOffice Amos Eaton 115Office hours Mon 930-1100AMTue 1100AM-1230PMThu 200-300PMKonstantin KuzminEmail kuzmik2rpieduOffice Amos Eaton 112Office hours TBDGra Addressing Modes. Department of Computer Science, Faculty of Science, Chiang Mai University. Outline. One-Dimensional Arrays. Addressing Modes. Two-Dimensional Arrays. Based Indexed Addressing Mode. 204231: Computer Organization and Architecture. The FLAGS Register. Department of Computer Science, Faculty of Science, Chiang Mai University. Outline. The FLAGS Register. Overflow. How Instruction Affect the Flags. 204231: Computer Organization and Architecture. Web marketing has come a long way and is one of the most effective forms of advertising. A website not only acts as an online repository of information but also acts as a hub for customers and clients to get in touch with your company. The benefits that Professional website designs can give to a business, especially in today’s highly competitive market, are numerous. This article is meant to make you aware of what web design is and why it is so important for your business. the Engineering . Industry. PRESENTED BY. Eng. GOUATER . LOIC. Objectives. Illustrate. how the use of computers in the engineering design . process. . improves. the . quality. of services in the . Computer Lab Rules. Report to class on time. If you are not in class when the bell rings. , report . to counselor for pass/detention. Computer Lab Rules. Stay in assigned seats. You are accountable for the computer which is assigned to you. Adeetya's Kitchen & Furniture in Pune offers exquisite handmade furniture designs with superior craftsmanship and modern, stylish appeal. https://adeetyas.com/factory-made-furniture-design-in-pune.php

Download Document

Here is the link to download the presentation.

"Computer Organization and Design"The content belongs to its owner. You may download and print it for personal use, without modification, and keep all copyright notices. By downloading, you agree to these terms.

Related Documents