PDF-High voltage drive to within 1.3 V of supply rails

Author : giovanna-bartolotta | Published Date : 2016-05-25

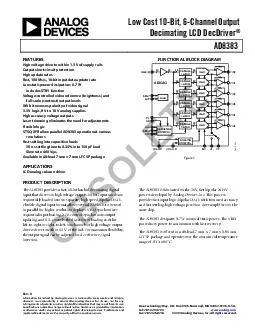

FEATURES Output shortcircuit protection High update rates Fast 100 Mss 10bit input data update rate Low static power dissipation 07 W Includes STBY function Voltagecontrolled

Presentation Embed Code

Download Presentation

Download Presentation The PPT/PDF document "High voltage drive to within 1.3 V of su..." is the property of its rightful owner. Permission is granted to download and print the materials on this website for personal, non-commercial use only, and to display it on your personal computer provided you do not modify the materials and that you retain all copyright notices contained in the materials. By downloading content from our website, you accept the terms of this agreement.

High voltage drive to within 1.3 V of supply rails: Transcript

FEATURES Output shortcircuit protection High update rates Fast 100 Mss 10bit input data update rate Low static power dissipation 07 W Includes STBY function Voltagecontrolled video refer. 5 Rails 30 and prior 5 Jammit and a JST naming gotcha 6 Rails 31 and above 7 An overview of the stack connecting Rails and Backbone 9 Setting up models Biasing in Synopsys. Andy . Whetzel. . University . of Virginia. 1. Agenda. Quick Background. FinFET . technology. Motivation. Supply-Biased. . D. esign. Proof-of-Concept Results. Challenge in Synopsys. Content and Language Objectives. Content Objective. SWBAT . look closely to discern a pattern or structure. (. Standards for Mathematical Practice 7. ). Language Objective. SWBAT use clear definitions in discussion with others and in their own reasoning. (. | @. RailsGirls_TI. | WWW.RAILSGIRLS.COM/TICINO. Lugano. , 29.03.2014. Ruby on Rails. INTRODUCTION. THE BASICS. THE BASICS – ROR. DEVELOPING THE APPLICATION. CONCLUSIONS. . 01. . Introduction. Rebecca Crabb and Blaine . Stancill. Ruby. Open-Source Programming Language. Created by Yukihiro Matsumoto. Blended parts of other languages. “I wanted a scripting language that was more powerful than Perl and more object-oriented than Python”. Mark Zhang. In this talk. Overview of Ruby on Rails. Core ideas. Show a tiny bit of example code. Touch on several general web development/ software development concepts. What is Ruby on Rails?. Ruby on Rails is an open source full-stack web framework.. Rails. : An introduction - . Who. . am. I?. Maciej Mensfeld. Presented . b. y. :. . Maciej Mensfeld. RoR. : An introduction . maciej@mensfeld.pl. dev.mensfeld.pl. github.com. /. mensfeld. senior . Testing. and . Performance Analysis. 报告人:. René Peter Paul . Smeets. . professor . at Eindhoven . University. 时间:. 11. 月. 26. 日 上午. 9:00-11:00. 地点. :. 西. 主楼. Ruby on Rails is a server side backend platform that uses CSS, JavaScript and HTML and combines all of these with Ruby language to create web apps and web servers. At ARKA, we understand the value of Ruby on Rails and providing a lot ROR Web Development advantages. In this Infograph one can know what are the pros and cons of ROR. https://www.arkasoftwares.com/rubyonrails-development.html P. ulsed loads. Part - 2. Presented by: Sanjay Pithadia. SEM – Industrial Systems, Medical Sector. Challenge to Solve . Floating the regulators to support high voltages. 2. Need of Floating Regulators. P. ulsed loads. Part - 3. Presented by: Sanjay Pithadia. SEM – Industrial Systems, Medical Sector. Challenge to Solve. Scaling Voltage and Current using standard voltage regulators and MOSFETs. 2. Voltage Scaling – to support Higher Input Voltage. A business really is only as good as the people who work in it. And a business software application is certainly only as good as the people who create and maintain it. That means that any company trying to fill Ruby on Rails developer jobs needs to go about doing so with care. ? . 体験会. 北海道大学 大学院理学院. 宇宙理学専攻. 荻原 弘尭. 目次. はじめに. Ruby on Rails(. 基本. ). 現在稼働中のサービスについての紹介. 今から始める.

Download Document

Here is the link to download the presentation.

"High voltage drive to within 1.3 V of supply rails"The content belongs to its owner. You may download and print it for personal use, without modification, and keep all copyright notices. By downloading, you agree to these terms.

Related Documents