PPT-Previously, we discussed about “prototyping” code for S

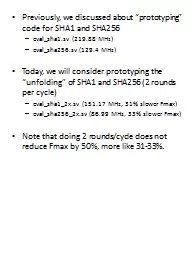

evalsha1sv 21988 MHz evalsha256sv 1294 MHz Today we will consider prototyping the unfolding of SHA1 and SHA256 2 rounds per cycle evalsha12xsv 15117 MHz 31 slower

Download Presentation

"Previously, we discussed about “prototyping” code for S" is the property of its rightful owner. Permission is granted to download and print materials on this website for personal, non-commercial use only, provided you retain all copyright notices. By downloading content from our website, you accept the terms of this agreement.

Presentation Transcript

Transcript not available.