PDF-The future technology for NAND flash

Author : trish-goza | Published Date : 2017-04-01

Copyright

Presentation Embed Code

Download Presentation

Download Presentation The PPT/PDF document "The future technology for NAND flash" is the property of its rightful owner. Permission is granted to download and print the materials on this website for personal, non-commercial use only, and to display it on your personal computer provided you do not modify the materials and that you retain all copyright notices contained in the materials. By downloading content from our website, you accept the terms of this agreement.

The future technology for NAND flash: Transcript

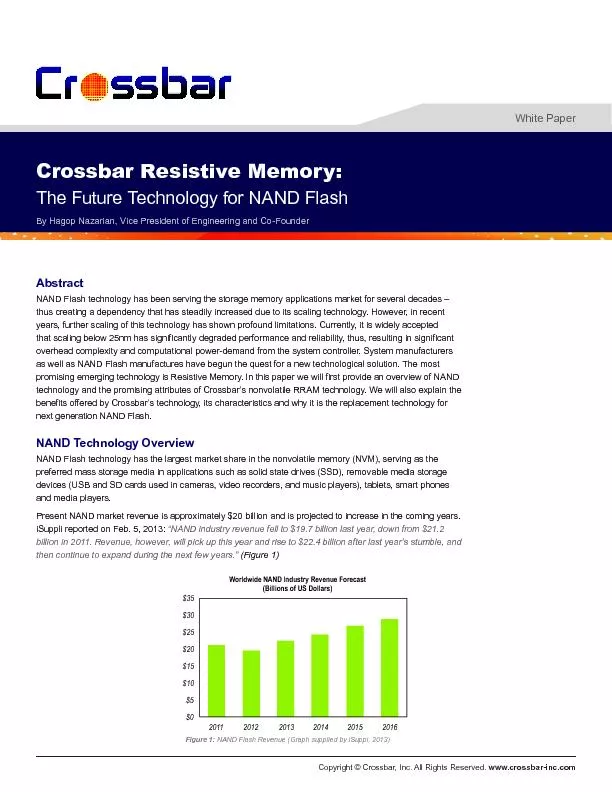

Copyright. Computing on Private Data. Ten H Lai. Ohio State University. Agenda. Computing on private data. Fully . homomorphic. encryption . (FHE). Gentry’s bootstrapping theorem. Our result. FHE: The Holy Grail of Cryptography. @ Micron.com. Flash Memory Technology Direction . Jim Cooke. Director of Applications Engineering. Memory Products Group. Micron Technology, Inc.. Agenda . Mass Storage . HDD, HHD, SSD. How Flash can Benefit Drives. FLASH. Yaakov (J) Stein. Types of Memory. By memory we mean any device that stores bits of information. Volatile memory. requires voltage (. and perhaps refresh. ) to maintained information. most frequently used for RAM. Nikhil Nichani. Francis Perez. Business Summary. Micron Technology, based in Boise, Idaho, engages in manufacturing and marketing of semiconductor devices worldwide. The company’s product line include Dynamic Random Access Memory(DRAM), Solid-State Drive(SSD), and Flash Memory(NAND and NOR). Micron’s products are used in many electronic applications such as personal computers, memory cards, mobile phones, USB storage devices, digital cameras, and MP3 players. Micron has assembling facilities in the United States, Asia, Middle-East, and Europe, and is a major player in the international markets with strong sales in China. In May, 2010, Micron completed the acquisition of . Subprograms. IAY 0600. Digital Systems Design. Alexander Sudnitson. Tallinn University of Technology. 1. 2. Subprograms. A subprogram is an encapsulated sequence of . sequential . statements that define an algorithm. The algorithm uses the values of input parameters, passed to the subprogram when it is called, to compute results or cause some desired effect. The actual code for a subprogram appears only once in the text of a program. However, the subprogram can be executed by calling it from anywhere in the program. . Experimental Analysis, Exploits, and Mitigation Techniques. HPCA Session 3A – Monday, 3:15 . pm. , Salon F. 128GB. NAND . Flash. 256GB. NAND Flash. NAND flash scaling: . shrink size. . of each . flash cell, . (and Security) Issues of DRAM and NAND Flash Scaling. Onur Mutlu. omutlu@gmail.com. http://users.ece.cmu.edu/~omutlu. /. HPCA Memory . R. eliability Workshop. March 13, 2016. Limits of Charge Memory. Memory: Characterization. , Optimization, and . Recovery. Yixin Luo. yixinluo@cmu.edu. (joint work with Yu Cai, . Erich . F. Haratsch, Ken Mai, Onur Mutlu). 1. Presented in the best paper session at HPCA 2015. Flash Memory Programming:. Experimental Analysis, Exploits,. and Mitigation Techniques. Yu Cai, . Saugata Ghose. , Yixin Luo,. Ken Mai, Onur Mutlu, Erich F. . Haratsch. February 6, 2017. Executive Summary. FLIN: Enabling Fairness and Enhancing Performance in Modern NVMe Solid State Drives August 7, 2019 Santa Clara, CA Saugata Ghose Carnegie Mellon University Executive Summary Modern solid-state drives (SSDs) use new storage protocols Jim Cooke. Director of Applications Engineering. Memory Products Group. Micron Technology, Inc.. Agenda . Mass Storage . HDD, HHD, SSD. How Flash can Benefit Drives. Hybrid, . ReadyBoost. , Robson, SSD. Lecture 5. Flash File Systems. September . 11. th. , . 2023. John . Kubiatowicz. Electrical Engineering and Computer Sciences. University of California, Berkeley. http://www.eecs.berkeley.edu/~kubitron/cs262. Vinod Ganapathy . Material drawn from the OSTEP book. 1. What are flash chips, aka SSDs?. Flash chips are designed to store one or more bits in a single transistor. single-level cell (SLC) flash, only a single bit is stored within a transistor (i.e., 1 or 0). Kim. 2. , . Myoungjun. Chun. 2. , . Lois Orosa. 1. , . Jihong. Kim. 2. , and . Onur. Mutlu. 1. ASPLOS 2021 (Session 17: Solid State Drives). Reducing Solid-State Drive Read Latency. by Optimizing Read-Retry.

Download Document

Here is the link to download the presentation.

"The future technology for NAND flash"The content belongs to its owner. You may download and print it for personal use, without modification, and keep all copyright notices. By downloading, you agree to these terms.

Related Documents