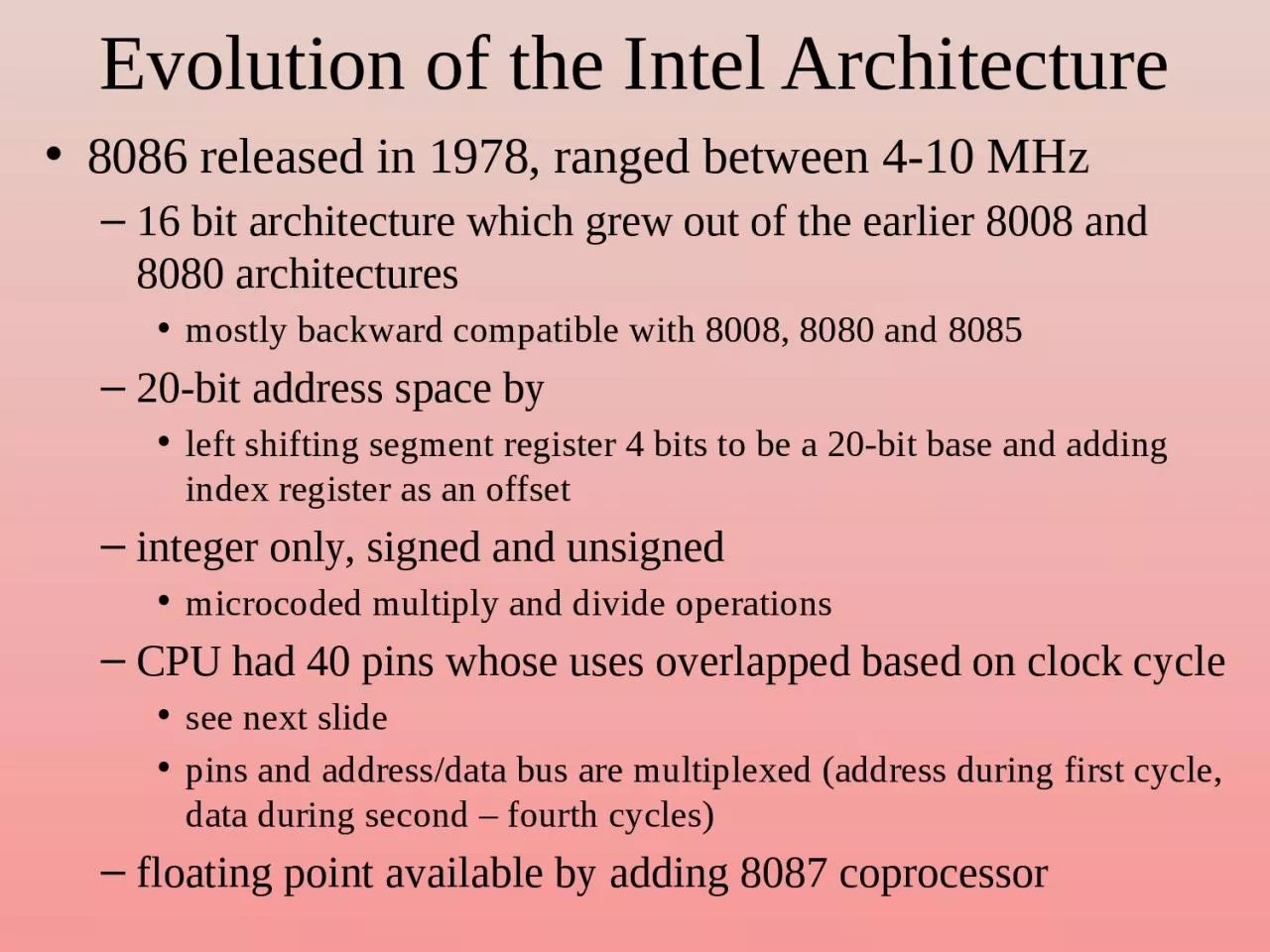

PPT-Evolution of the Intel Architecture

8086 released in 1978 ranged between 410 MHz 16 bit architecture which grew out of the earlier 8008 and 8080 architectures mostly backward compatible with 8008 8080

Download Presentation

"Evolution of the Intel Architecture" is the property of its rightful owner. Permission is granted to download and print materials on this website for personal, non-commercial use only, provided you retain all copyright notices. By downloading content from our website, you accept the terms of this agreement.

Presentation Transcript

Transcript not available.