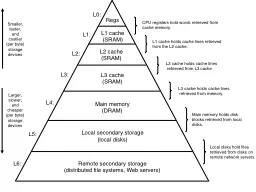

PPT-Regs L1 cache (SRAM) Main memory

DRAM Local secondary storage local disks Larger slower and cheaper per byte storage devices Remote secondary storage distributed file systems Web servers Local disks

Download Presentation

"Regs L1 cache (SRAM) Main memory" is the property of its rightful owner. Permission is granted to download and print materials on this website for personal, non-commercial use only, provided you retain all copyright notices. By downloading content from our website, you accept the terms of this agreement.

Presentation Transcript

Transcript not available.