PDF-MT TUTORIAL Aperture Time Aperture Ji tter Aperture Delay Time Removing the Confusion by Walt Kester INTRODUCTION Perhaps the most misunderstood and misused ADC and sampleandhold or trackandhold spec

SO

pasty-toler

Published 2015-02-17 | 6824 Views

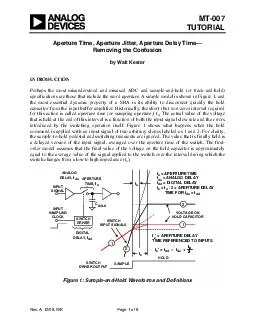

A simple model is shown in Figure 1 and the most essential dynamic property of a SHA is its ability to disconnect quickly the hold capacitor from the input buffer

Download Presentation

Download Presentation The PPT/PDF document "MT TUTORIAL Aperture Time Aperture Ji tt..." is the property of its rightful owner. Permission is granted to download and print the materials on this website for personal, non-commercial use only, and to display it on your personal computer provided you do not modify the materials and that you retain all copyright notices contained in the materials. By downloading content from our website, you accept the terms of this agreement.