PPT-Extended Memory Controller and the MPAX registers And Cache

Author : giovanna-bartolotta | Published Date : 2017-07-19

Multicore programming and Applications February 19 2013 Agenda A little reminder of the 6678 Purpose of MPAX part of XMC CorePac MPAX registers CorePac MAR registers

Presentation Embed Code

Download Presentation

Download Presentation The PPT/PDF document "Extended Memory Controller and the MPAX ..." is the property of its rightful owner. Permission is granted to download and print the materials on this website for personal, non-commercial use only, and to display it on your personal computer provided you do not modify the materials and that you retain all copyright notices contained in the materials. By downloading content from our website, you accept the terms of this agreement.

Extended Memory Controller and the MPAX registers And Cache: Transcript

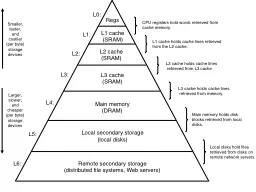

Multicore programming and Applications February 19 2013 Agenda A little reminder of the 6678 Purpose of MPAX part of XMC CorePac MPAX registers CorePac MAR registers Teranet Access MPAX registers. Computer System Overview. Patricia Roy. Manatee Community College, Venice, FL. ©2008, Prentice Hall. Operating Systems:. Internals and Design Principles, 6/E. William Stallings. Operating System. Exploits the hardware resources of one or more processors. CS448. 2. What is Cache Coherence?. Two processors can have two different values for the same memory location. Write Through Cache. 3. Terminology. Coherence. Defines what values can be returned by a read. Mark Gebhart. 1,2 . Stephen W. Keckler. 1,2. Brucek Khailany. 2. Ronny Krashinsky. 2. . William J. Dally. 2,3. 1. The University of Texas at Austin . 2. NVIDIA . 3. Stanford University. Methodology. Aanjhan . Ranganathan (. ETH Zurich. ). , . Ali . Galip. . Bayrak. (. EPFL. ), . Theo . Kluter. . (. BFH. ), . Philip . Brisk (. UC Riverside. ), . Edoardo. . Charbon. (. TU Delft. ), Paolo . Ienne. 1. The University of Texas at Austin. The University of Texas at Austin. Ali Shafiee. , A. . Gundu. , M. . Shevgoor. , R. . Balasubramonian. and M. . Tiwari. Shared Memory Controller. Core1. $. MC. Core0. (DRAM). Local secondary storage. (local disks). Larger, . slower, . and . cheaper . (per byte). storage. devices. Remote secondary storage. (distributed file systems, Web servers). Local disks hold files retrieved from disks on remote network servers.. Table 4.1 . Key . Characteristics of Computer Memory Systems. . © 2016 Pearson Education, Inc., Hoboken, NJ. All rights reserved.. Characteristics of Memory Systems. Location. Refers to whether memory is internal and external to the computer. Managed jointly by CPU hardware and the operating system (OS). Programs share main memory. Each gets a private virtual address space holding its frequently used code and data. Protected from other programs. Lecture for CPSC 5155. Edward Bosworth, Ph.D.. Computer Science Department. Columbus State University. The Simple View of Memory. The simplest view of memory is . that presented . at the ISA (Instruction Set Architecture) level. At this level, memory is a . Virtual Memory Use main memory as a “cache” for secondary (disk) storage Managed jointly by CPU hardware and the operating system (OS) Programs share main memory Each gets a private virtual address space holding its frequently used code and data Extended Metaphor An extended metaphor is a metaphor that unfolds across multiple lines or even paragraphs of a text, making use of multiple interrelated metaphors within an overarching one. Definition of Extended Metaphor 2. Educational objectives The MESI protocol simulator is widely used in several courses about Computer Architecture, Computer Design and Multiprocessor Systems in the University of Cordoba. The syllab The basic objective of a computer system is to increase the speed of computation. Likewise, the basic objective of a memory system is to provide fast, uninterrupted access by the processor to the memory such that, the processor can operate at its expected speed. . Mohammad Laghari and Didem Unat. 1. SBAC-PAD 2017 @ Campinas, Brazil 17-20 October 2017. https://parcorelab.ku.edu.tr. Image taken from: http://www.amd.com/en/technologies/hbm. Introduction. To overcome memory bandwidth limitations, multiple memories with different characteristics are introduced.

Download Document

Here is the link to download the presentation.

"Extended Memory Controller and the MPAX registers And Cache"The content belongs to its owner. You may download and print it for personal use, without modification, and keep all copyright notices. By downloading, you agree to these terms.

Related Documents